การออกแบบวงจร 3 to 8 decorder

วัตถุประสงค์ในการทดลอง

1. ฝึกการออกแบบวงจร 3 to 8 decorder โดยใช้โปรแกรม Quartus

2. สามารถออกแบบวงจรโดยใช่ลอจิเกตพื้นฐาน และใช้ภาษา VHDL ในการออกแบบได้

3. สามารถทดลองกับบอร์ด FPGA ได้อย่างถูกต้องเหมาะสมได้

อุปกรณ์ที่ใช้ในการทดลอง

1. บอร์ด Altera FPGA Board (WARRIOR CYCLONE3 DEV) 1 บอร์ด

2. สายดาวน์โหลด ByteBlaster II และ USB Blaster 1 สาย

โจทย์

1) จงออกแบบวงจร 3-to-8 decoder มีทำงานตามข้อกำหนดต่อไปนี้

- มีอินพุต A(2:0) และเอาต์พุต Y(7:0)

ถ้า A(2:0) = "000" จะได้ Y(7:0) = "00000001"

ถ้า A(2:0) = "001" จะได้ Y(7:0) = "00000010"

ถ้า A(2:0) = "010" จะได้ Y(7:0) = "00000100"

.......

ถ้า A(2:0) = "111" จะได้ Y(7:0) = "10000000"

- มีอินพุต A(2:0) และเอาต์พุต Y(7:0)

ถ้า A(2:0) = "000" จะได้ Y(7:0) = "00000001"

ถ้า A(2:0) = "001" จะได้ Y(7:0) = "00000010"

ถ้า A(2:0) = "010" จะได้ Y(7:0) = "00000100"

.......

ถ้า A(2:0) = "111" จะได้ Y(7:0) = "10000000"

- อินพุต A(2:0) ให้ใช้สวิตช์เลื่อน (Slide Switches) บนบอร์ด FPGA

- เอาต์พุต Y(7:0) ให้ใช้ LEDs บนบอร์ด FPGA

- เอาต์พุต Y(7:0) ให้ใช้ LEDs บนบอร์ด FPGA

การออกแบบวงจร ให้ใช้วิธีดังต่อไปนี้ (สร้าง Design Project สำหรับแต่ละกรณี)

- ใช้วิธีวาดวงจร โดยใช้ลอจิกเกตพื้นฐาน อย่างเช่น AND, OR, NOT

- ใช้ภาษา VHDL ในการออกแบบ

- ทดลองในบอร์ด FPGA และเขียนรายงานการทดลอง

ขั้นตอนและผลการทดลอง

1) เตรียมอุปกรณ์

Altera FPGA Board

ByteBlaster II และ USB Blaster

โปรแกรม Altera Quartus II Web Edition

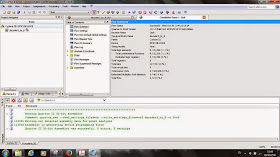

2.) วาดวงจร 3 to 8 decorder โดยใช้ลอจิกเกตพื้นฐาน อย่างเช่น AND, OR, NOT

ด้วยโปรแกรม Quartus

3.) ใช้ภาษา VHDL ในการออกแบบวงจรตามที่โจทย์กำหนด

1.

สร้างโปรเจคสำหรับการทดลอง

โดยทำการเลือก

-

เลือกชิปที่ตรงกับบอร์ด

FPGA เป็น EP3C10E144C8

-

Device Family ตระกูล Cyclone

III

-

Design synthesis เลือก

ModelSim-Altera สำหรับเครื่องมือการจำลองการทำงาน (Simulation)

โดยใช้ภาษา VHDL

code

library ieee, work;

use ieee.std_logic_1164.all;

use ieee.numeric_std.all;

entity tb decoder tb_decoder3_to_8 is

end tb_decoder3_to_8;

architecture testbench of tb_decoder3_to_8 is

component decoder3_to_8 is

port(

I : in std_logic_vector( 2 downto 0 );

O : out std_logic_vector( 7 downto 0 ) );

end component;

signal t_I : std_logic_vector( 2 downto 0 );

signal t_O : std_logic_vector( 7 downto 0 );

begin

DUT: decoder decoder3_to_8 port map( I => t I_ , O => t O_ );

process begin

t_I <= "000";

for i in 0 to 7 loop

t_I <= std_logic_vector( to_unsigned(i, 3) );

wait for 100 ns;

end loop;

end process;

end testbench;

4.) ทำการ Analysis & Synthetic เพื่อวิเคราะห์และสังเคราะห์วงจรดิจิทัลจากโค้ด

VHDL

5.) กำหนดหมายเลขขาอินพุต-เอาต์พุตสำหรับวงจร โดยใช้คำสั่ง Pin Planner

ถ้ามีการใช้ LED จากบอร์ด FPGA ให้เพิ่มชื่อสัญญาณ LED_54 ที่ขา PIN_54 และกำหนดให้เป็น

As output, driving GND โดย ขา 54 ต่ออยู่กับสัญญาณ LED_54 ที่เป็นตัวควบคุมการทำงานของ LEDs บนบอร์ดทดลอง

FPGA ที่ใช้

6.) ทำการ Fitter และ Assembler

7.) ใช้คำสั่ง Programmer เพื่อทำการรันโค้ดที่ได้บนวงจร

FPGA Board

8.) นำไปทดลองบนบอร์ด FPGA

จากการทดลองข้อที่ 3 :